TMS320VC5509AZAY Digitální signálové procesory a řadiče – DSP, DSC digitální signálový procesor s pevným bodem 179-NFBGA -40 až 85

♠ Popis produktu

| Atribut produktu | Hodnota atributu |

| Výrobce: | Texas Instruments |

| Kategorie produktů: | Digitální signálové procesory a řadiče - DSP, DSC |

| RoHS: | Podrobnosti |

| Produkt: | DSP |

| Série: | TMS320VC5509A |

| Styl montáže: | SMD/SMT |

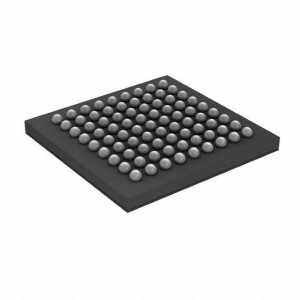

| Balíček/pouzdro: | NFBGA-179 |

| Jádro: | C55x |

| Počet jader: | 1 jádro |

| Maximální frekvence hodin: | 200 MHz |

| Paměť instrukcí mezipaměti L1: | - |

| Datová paměť mezipaměti L1: | - |

| Velikost paměti programu: | 64 kB |

| Velikost datové paměti RAM: | 256 kB |

| Provozní napájecí napětí: | 1,6 V |

| Minimální provozní teplota: | - 40 C |

| Maximální provozní teplota: | + 85 C |

| Obal: | Zásobník |

| Značka: | Texas Instruments |

| Typ instrukce: | Pevný bod |

| Typ rozhraní: | I2C |

| Citlivé na vlhkost: | Ano |

| Typ produktu: | DSP - Digital Signal Processors & Controllers |

| Tovární množství balení: | 160 |

| Podkategorie: | Vestavěné procesory a řadiče |

| Napájecí napětí - Max: | 1,65 V |

| Napájecí napětí - Min: | 1,55 V |

| Časovače hlídacího psa: | Watchdog Timer |

♠ TMS320VC5509A digitální signálový procesor s pevným bodem

Procesor digitálního signálu (DSP) TMS320VC5509A je založen na jádru procesoru CPU generace TMS320C55x DSP.Architektura C55x™ DSP dosahuje vysokého výkonu a nízké spotřeby díky zvýšenému paralelismu a úplnému zaměření na snížení ztrátového výkonu.CPU podporuje vnitřní strukturu sběrnice, která se skládá z jedné programové sběrnice, tří sběrnic pro čtení dat, dvou sběrnic pro zápis dat a dalších sběrnic vyhrazených pro periferní a DMA činnost.Tyto sběrnice poskytují schopnost provádět až tři čtení dat a dva zápisy dat v jednom cyklu.Paralelně může řadič DMA provádět až dva přenosy dat za cyklus nezávisle na aktivitě CPU.

C55x CPU poskytuje dvě multiply-accumulate (MAC) jednotky, z nichž každá je schopna 17bitové x 17bitové násobení v jediném cyklu.Centrální 40bitová aritmetická/logická jednotka (ALU) je podporována další 16bitovou ALU.Použití ALU je pod kontrolou instrukční sady, což poskytuje schopnost optimalizovat paralelní činnost a spotřebu energie.Tyto prostředky jsou spravovány v adresové jednotce (AU) a datové jednotce (DU) CPU C55x.

Generace C55x DSP podporuje sadu instrukcí s proměnnou šířkou bajtů pro lepší hustotu kódu.Instrukční jednotka (IU) provádí 32bitové načítání programu z interní nebo externí paměti a řadí instrukce pro programovou jednotku (PU).Programová jednotka dekóduje instrukce, směruje úkoly do zdrojů AU a DU a spravuje plně chráněný kanál.Schopnost prediktivního větvení zabraňuje proplachům potrubí při provádění podmíněných instrukcí.

Univerzální vstupní a výstupní funkce a 10bitové A/D poskytují dostatek pinů pro stav, přerušení a bitové I/O pro LCD, klávesnice a mediální rozhraní.Paralelní rozhraní pracuje ve dvou režimech, buď jako slave k mikrokontroléru pomocí HPI portu nebo jako paralelní rozhraní médií pomocí asynchronního EMIF.Sériová média jsou podporována prostřednictvím dvou periferních zařízení MultiMedia Card/Secure Digital (MMC/SD) a tří zařízení McBSP.

Sada periferií 5509A obsahuje externí paměťové rozhraní (EMIF), které poskytuje bezlepkový přístup k asynchronním pamětem, jako jsou EPROM a SRAM, a také k vysokorychlostním pamětem s vysokou hustotou, jako je synchronní DRAM.Mezi další periferie patří Universal Serial Bus (USB), hodiny reálného času, hlídací časovač, I2C multi-master a slave rozhraní.Tři plně duplexní vícekanálové vyrovnávací sériové porty (McBSP) poskytují bezlepkové rozhraní pro řadu průmyslových standardních sériových zařízení a vícekanálovou komunikaci s až 128 samostatně povolenými kanály.Vylepšené rozhraní hostitelského portu (HPI) je 16bitové paralelní rozhraní používané k poskytování přístupu hostitelského procesoru k 32 kB vnitřní paměti na 5509A.HPI může být konfigurováno buď v multiplexovaném nebo nemultiplexním režimu, aby poskytovalo bezlepkové rozhraní pro širokou škálu hostitelských procesorů.Řadič DMA zajišťuje pohyb dat pro šest nezávislých kanálových kontextů bez zásahu CPU a poskytuje propustnost DMA až dvou 16bitových slov za cyklus.Součástí jsou také dva univerzální časovače, až osm vyhrazených univerzálních I/O (GPIO) pinů a generování hodin s digitální fázovou smyčkou (DPLL).

Model 5509A je podporován oceňovaným eXpressDSP™, integrovaným vývojovým prostředím Code Composer Studio™ (IDE), DSP/BIOS™, algoritmickým standardem Texas Instruments a největší sítí třetích stran v oboru.Code Composer Studio IDE obsahuje nástroje pro generování kódu včetně C Compiler a Visual Linker, simulátor, RTDX™, emulační ovladače zařízení XDS510™ a vyhodnocovací moduly.5509A je také podporována knihovnou C55x DSP Library, která obsahuje více než 50 základních softwarových jader (FIR filtry, IIR filtry, FFT a různé matematické funkce) a také knihovny pro podporu čipů a desek.

Jádro TMS320C55x DSP bylo vytvořeno s otevřenou architekturou, která umožňuje přidání hardwaru specifického pro aplikaci pro zvýšení výkonu na konkrétních algoritmech.Hardwarová rozšíření na 5509A dosahují dokonalé rovnováhy mezi výkonem pevných funkcí a programovatelnou flexibilitou při dosažení nízké spotřeby energie a nákladů, které bylo tradičně na trhu videoprocesorů obtížné najít.Rozšíření umožňují 5509A poskytovat výjimečný výkon video kodeku s více než poloviční šířkou pásma dostupnou pro provádění dalších funkcí, jako je konverze barevného prostoru, operace uživatelského rozhraní, zabezpečení, TCP/IP, rozpoznávání hlasu a převod textu na řeč.Výsledkem je, že jediný DSP 5509A může napájet většinu přenosných digitálních video aplikací s rezervou na zpracování.Další informace naleznete v TMS320C55x Hardware Extensions for Image/Video Applications Programmer's Reference (číslo literatury SPRU098).Další informace o používání knihovny DSP Image Processing Library naleznete v TMS320C55x Image/Video Processing Library Programmer's Reference (číslo literatury SPRU037).

• Vysoce výkonný, nízkoenergetický procesor digitálního signálu TMS320C55x™ s pevným bodem

− 9,26-, 6,95-, 5-ns Doba cyklu instrukcí

− Taktovací frekvence 108-, 144-, 200 MHz

− Jedna/dvě instrukce provedené za cyklus

− Duální multiplikátory [až 400 milionů multiplikátorů za sekundu (MMACS)]

− Dvě aritmetické/logické jednotky (ALU)

− Tři interní sběrnice dat/čtení operandů a dvě interní sběrnice dat/zápis operandů

• 128K x 16bitová RAM na čipu, složená z:

− 64 kB bajtů paměti RAM s duálním přístupem (DARAM) 8 bloků 4K × 16 bitů

− 192 kB bajtů paměti RAM s jedním přístupem (SARAM) 24 bloků 4K × 16bitů

• 64 000 bajtů ROM na čipu v jednom stavu (32 kB × 16 bitů)

• 8M × 16bitový maximální adresovatelný externí paměťový prostor (synchronní DRAM)

• 16bitová paměť externí paralelní sběrnice s podporou buď:

− Rozhraní externí paměti (EMIF) s funkcemi GPIO a rozhraním Glueless pro:

- Asynchronní statická RAM (SRAM)

− Asynchronní EPROM

- Synchronní DRAM (SDRAM)

− 16bitové paralelní vylepšené rozhraní hostitelského portu (EHPI) s funkcemi GPIO

• Programovatelné řízení nízké spotřeby šesti funkčních domén zařízení

• Logika emulace založená na skenování na čipu

• Periferní zařízení na čipu

− Dva 20bitové časovače

− Watchdog Timer

− Šestikanálový řadič přímého přístupu do paměti (DMA).

− Tři sériové porty podporující kombinaci:

− Až 3 vícekanálové sériové porty s vyrovnávací pamětí (McBSP)

− Až 2 rozhraní MultiMedia/Secure Digital Card

− Programovatelný generátor hodin smyčky s fázovým závěsem

− Sedm (LQFP) nebo osm (BGA) univerzálních I/O (GPIO) kolíků a jeden univerzální výstupní kolík (XF)

− USB Full-Speed (12 Mbps) Slave port podporující hromadné, přerušované a izochronní přenosy

− Inter-Integrated Circuit (I2C) Multi-Master a Slave rozhraní

− Hodiny reálného času (RTC) s krystalovým vstupem, samostatnou doménou hodin, samostatným napájecím zdrojem

− 4kanálový (BGA) nebo 2kanálový (LQFP) 10bitová postupná aproximace A/D

• IEEE Std 1149.1† (JTAG) Boundary Scan Logic

• Balíčky:

− 144-terminálový nízkoprofilový čtyřplošný plochý balíček (LQFP) (přípona PGE)

− 179-terminálový MicroStar BGA™ (Ball Grid Array) (GHH Suffix)

− 179-terminálový bezolovnatý MicroStar BGA™ (Ball Grid Array) (Suffix ZHH)

• 1,2-V jádro (108 MHz), 2,7-V – 3,6-VI/O

• 1,35-V jádro (144 MHz), 2,7-V – 3,6-VI/O

• 1,6-V jádro (200 MHz), 2,7-V – 3,6-VI/O

• Hybridní, elektrický a hnací systém (EV/HEV)

- Systém správy baterie (BMS)

– Palubní nabíječka

– Trakční měnič

– DC/DC měnič

– Startér/generátor