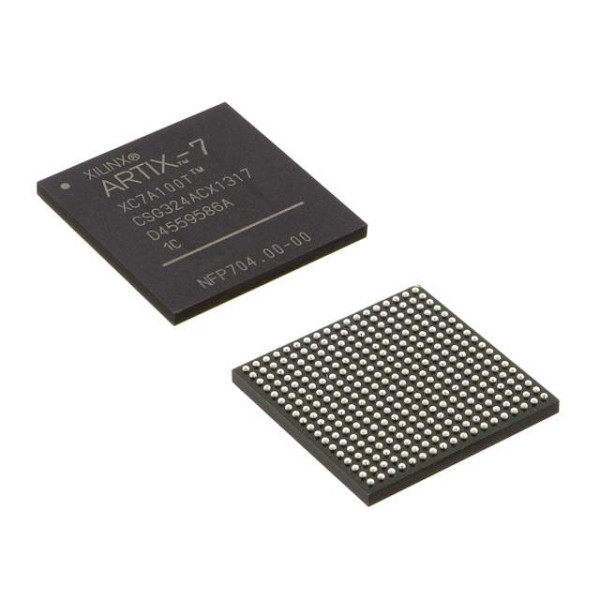

XC7A50T-2CSG324I FPGA – programovatelné hradlové pole XC7A50T-2CSG324I

♠ Popis produktu

| Atribut produktu | Hodnota atributu |

| Výrobce: | Xilinx |

| Kategorie produktů: | FPGA - Field Programmable Gate Array |

| Série: | XC7A50T |

| Počet logických prvků: | 52160 LE |

| Počet I/O: | 210 I/O |

| Napájecí napětí - Min: | 0,95 V |

| Napájecí napětí - Max: | 1,05 V |

| Minimální provozní teplota: | - 40 C |

| Maximální provozní teplota: | + 100 C |

| Rychlost přenosu dat: | - |

| Počet vysílačů a přijímačů: | - |

| Styl montáže: | SMD/SMT |

| Balíček / pouzdro: | CSBGA-324 |

| Značka: | Xilinx |

| Distribuovaná RAM: | 600 kbit |

| Embedded Block RAM - EBR: | 2700 kbit |

| Citlivé na vlhkost: | Ano |

| Počet bloků logického pole – LAB: | 4075 LAB |

| Provozní napájecí napětí: | 1 V |

| Typ produktu: | FPGA - Field Programmable Gate Array |

| Tovární množství balení: | 1 |

| Podkategorie: | Programovatelné logické integrované obvody |

| Jméno výrobku: | Artix |

| Jednotková hmotnost: | 1 unce |

♠ FPGA řady Xilinx® 7 se skládají ze čtyř rodin FPGA, které řeší kompletní řadu systémových požadavků, od nízkých nákladů, malých rozměrů, nákladově citlivých, velkoobjemových aplikací až po ultra high-end šířku pásma konektivity, logickou kapacitu a zpracování signálu. schopnost pro nejnáročnější vysoce výkonné aplikace

FPGA řady Xilinx® 7 se skládají ze čtyř rodin FPGA, které řeší kompletní řadu systémových požadavků, počínaje nízkou cenou, malým tvarovým faktorem, cenově citlivým, velkoobjemovým aplikacím až po ultra špičkovou šířku pásma konektivity, logickou kapacitu a schopnost zpracování signálu. pro nejnáročnější vysoce výkonné aplikace.Mezi FPGA řady 7 patří:

• Řada Spartan®-7: Optimalizováno pro nízkou cenu, nejnižší spotřebu a vysoký I/O výkon.K dispozici v levném, velmi malém balení pro nejmenší plochu PCB.

• Řada Artix®-7: Optimalizováno pro aplikace s nízkou spotřebou, které vyžadují sériové transceivery a vysokou DSP a logickou propustnost.Poskytuje nejnižší celkové náklady na kusovník pro vysoce výkonné a nákladově citlivé aplikace.

• Rodina Kintex®-7: Optimalizováno pro nejlepší poměr ceny a výkonu s 2x zlepšením ve srovnání s předchozí generací, což umožňuje novou třídu FPGA.

• Řada Virtex®-7: Optimalizováno pro nejvyšší výkon a kapacitu systému s dvojnásobným zlepšením výkonu systému.Zařízení s nejvyššími schopnostmi díky technologii vrstveného křemíkového propojení (SSI).

Postavené na nejmodernější, vysoce výkonné, nízkoenergetické (HPL), 28 nm, high-k metal gate (HKMG) procesní technologii, FPGA řady 7 umožňují bezkonkurenční zvýšení výkonu systému s 2,9 Tb/ s šířkou pásma I/O, kapacitou 2 miliony logických buněk a 5,3 TMAC/s DSP, přičemž spotřebují o 50 % méně energie než zařízení předchozí generace, což nabízí plně programovatelnou alternativu k ASSP a ASIC.

• Pokročilá vysoce výkonná logika FPGA založená na technologii skutečné 6vstupové vyhledávací tabulky (LUT) konfigurovatelné jako distribuovaná paměť.

• 36 Kb dvouportová bloková RAM s vestavěnou logikou FIFO pro ukládání dat na čipu.

• Vysoce výkonná technologie SelectIO™ s podporou rozhraní DDR3 až 1 866 Mb/s.

• Vysokorychlostní sériové připojení s vestavěnými multigigabitovými transceivery od 600 Mb/s do max.rychlosti 6,6 Gb/s až 28,05 Gb/s, nabízí speciální režim nízké spotřeby, optimalizovaný pro rozhraní čip-čip.

• Uživatelsky konfigurovatelné analogové rozhraní (XADC) obsahující duální 12bitové 1MSPS analogově-digitální převodníky s teplotními a napájecími senzory na čipu.

• DSP řezy s násobičem 25 x 18, 48bitovým akumulátorem a předsčítačkou pro vysoce výkonné filtrování, včetně optimalizovaného filtrování symetrických koeficientů.

• Výkonné dlaždice správy hodin (CMT), kombinující bloky fázového závěsu (PLL) a správce hodin ve smíšeném režimu (MMCM) pro vysokou přesnost a nízký jitter.

• Rychlé nasazení vestavěného zpracování s procesorem MicroBlaze™.

• Integrovaný blok pro PCI Express® (PCIe), až pro design x8 Gen3 Endpoint a Root Port.

• Široká škála možností konfigurace, včetně podpory komoditních pamětí, 256bitového šifrování AES s ověřováním HMAC/SHA-256 a vestavěné detekce a korekce SEU.

• Nízkonákladové balení flipchipu s drátovou vazbou, vyklápěcím čipem a vysokou integritou signálu nabízí snadnou migraci mezi členy rodiny v jednom balení.Všechny balíčky dostupné ve variantě bez Pb a vybrané balíčky ve variantě Pb.

• Navrženo pro vysoký výkon a nejnižší výkon s 28 nm, HKMG, HPL procesem, 1,0 V základním napětím a volitelným 0,9 V základním napětím pro ještě nižší výkon.